| Features | Applications |

| ? Small size (TO-8 package) allows mountingclose to detector. | ? Mass spectrometers |

| ? Power required is typically 6 mW. | ? Particle detection |

| ? Single power supply voltage. | ? Imaging |

| ? Output interface directly with CMOS and TTL logic. | ? Laboratory experiments |

| ? Input threshold is externally adjustable. | ? Research experiments |

| ? Analog monitor point. | ? Portable instrumentation |

| ? High reliability process. | ? Aerospace |

| ? 6 Pin SIP available as model A111F. | ? Medical electronics |

| ? One year warranty. | ? Electro-optical systems |

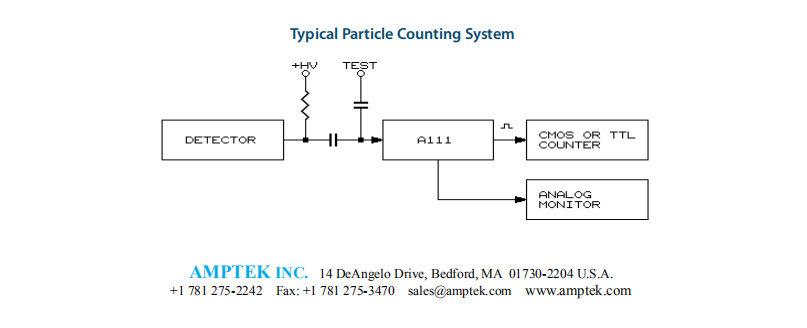

Overview

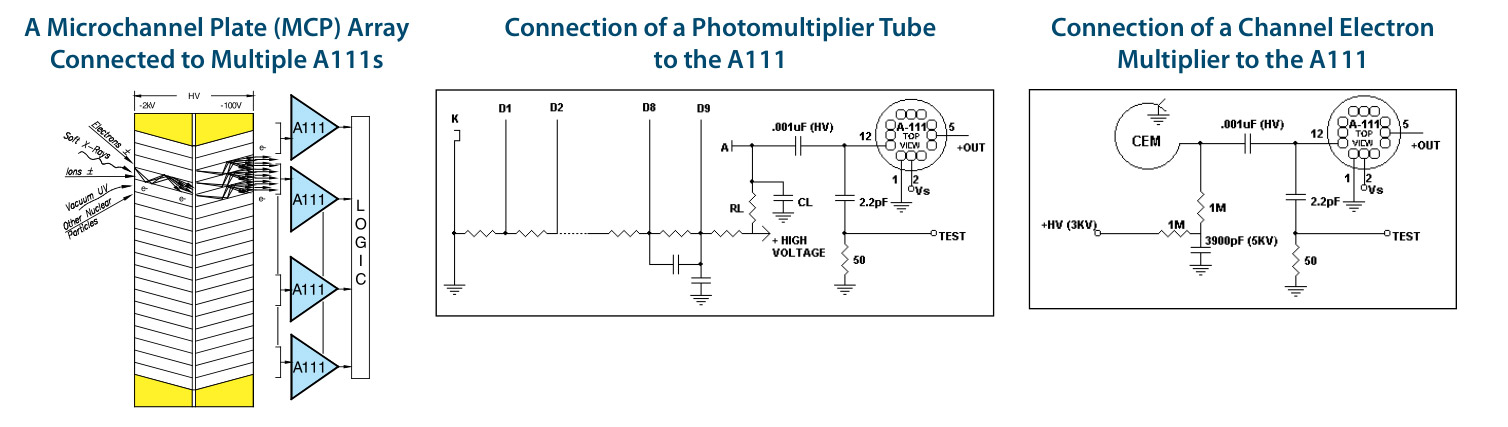

ModelA111 is a hybrid charge sensitive preamplifier, discriminator, and pulse shaper developed especially forinstrumentation employing microchannel plates(MCP), channel electron multipliers(CEM), photomultipliers,proportional counters and other low capacitance charge producing detectors in the pulse counting mode.

Test Conditions: (V s = +5 V, T = +25 °C)

INPUT CHARACTERISTICS Threshold

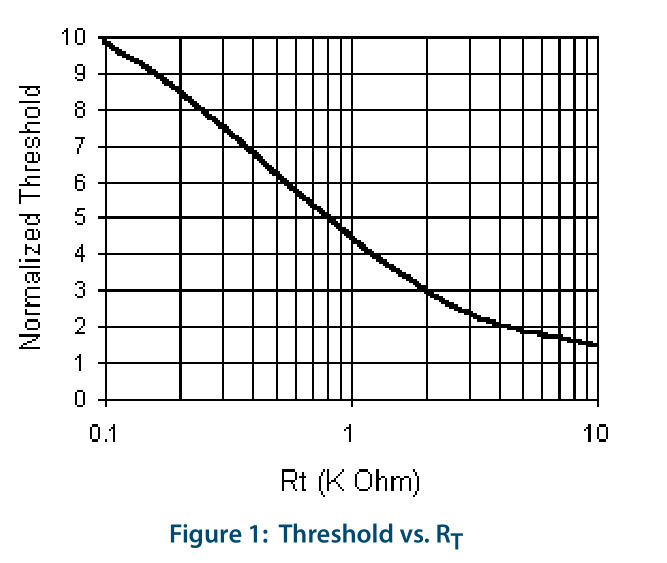

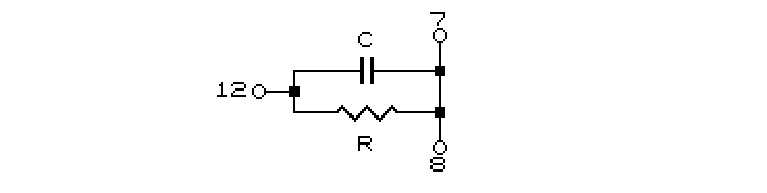

Model A111 has a nominal threshold referred to the input of 8 x 10 -15 coulomb.This is equivalent to 5 x 10 4 electrons. The threshold can be increased by the additionof a resistor between Pins 7 and 8. Shorting these Pins together produces the maximum

increase (approximately 10x). See Figure 1.

Stability

+5%, -2% of +25 oC threshold, 0 to +50 oC.

Supply voltage

Threshold supply voltage coefficient:-0.8% / V typical

Noise (typical)

4.4 x 10 -16 coulombs RMS; 5.5% of nominal threshold

Noise Slope(typical)

9 x 10 -17 coulombs RMS/pF

Detector Capacitance

0 to 250 pF

Protection

300 ? resistor in series with input followed by back-to-back diodes to ground

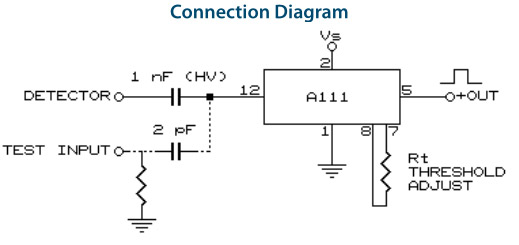

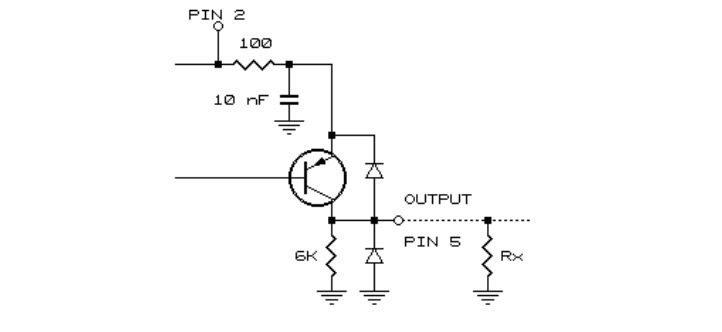

OUTPUT CHARACTERISTICS Pin 5 provides a positive output pulse capable of interfacing directly with CMOS and other logic. See Operating Notes.

Pin 7 provides a positive analog pulse output from the pream-plifier section just prior to the discriminator with a rise time of about 100 ns. At maximum sensitivity (no feedback resis-tor between Pins 7 and 8) the amplitude of this pulse is pro-portional to the input charge, A = 2.5 V/pC. At threshhold this will correspond to a 20 mV pulse. If a feedback resistor is used between Pins 7 and 8, the size of the analog pulse will be di-vided by the same threshold attenuation factor the feedback resistor produced. Example: If a 3 k? feedback resistor is used,the size of the analog pulse will be 1 V/pC. This output must be capacitively coupled to external circuitry and can be used to perform pulse height analysis. Near threshold, however, the

shape of the analog pulse will be effected by the firing of thediscriminator.

Pulse Characteristics

Risetime

25 ns

Falltime

220 ns with C LOAD = 5 pF; 90 ns with C LOAD =5 pF and R LOAD = 2 k?

Width

260 ns at threshold, 310 ns at 10x threshold,with C LOAD = 5 pF

Amplitude

4.7 V (approximately 95% of V s )

Protection

Diodes to ground and V s

GENERAL Count Rate

2.5 x 10 6 CPS periodic

Pulse Pair Resolution

1) Normal: 350 ns; two identical 10x threshold pulses.

2) Overload: 800 ns; 100x threshold followedby 10x threshold.

Operating Voltage

+4 to +10 VDC

Operating Cur-rent (typical)

1.3 mA quiescent.

1.4 mA @ 10 5 CPS.

1.9 mA @ 10 6 CPS

Operating current is essentially independent

of V s .

Temperature

-55 to +85 °C operational

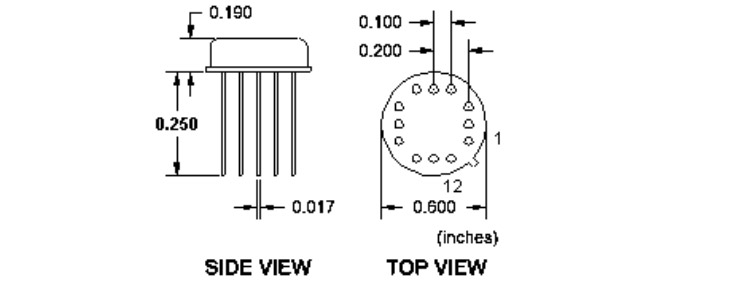

Package

12 Pin, TO-8 case. (6 Pin SIP available as A111F)

Weight

2.5 g

Screening

Amptek High Reliability

Warranty

One year

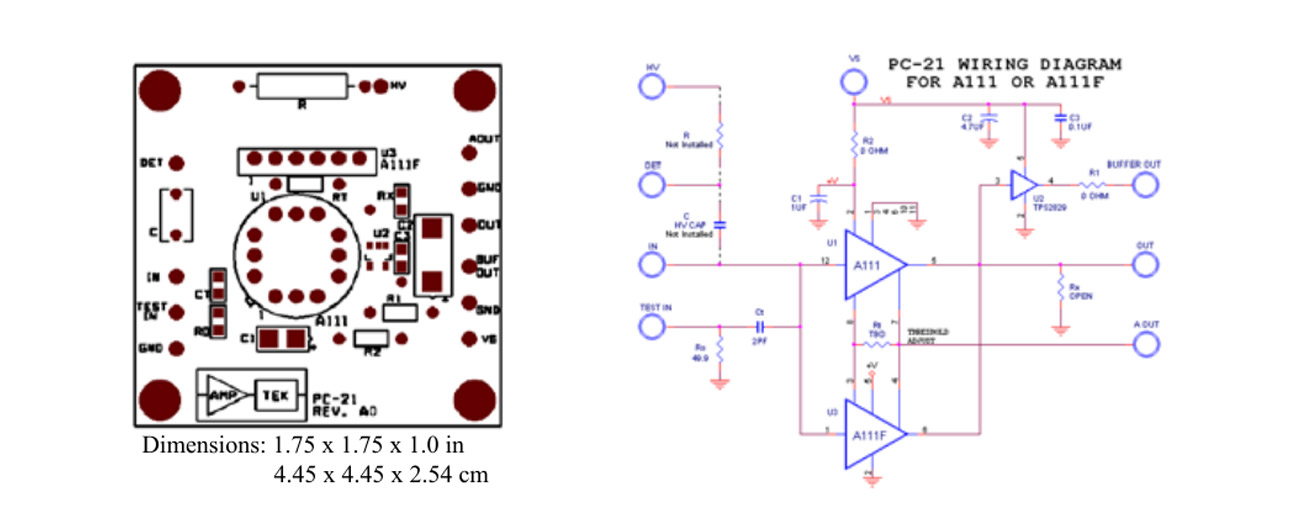

Test Board

PC-21

Vacuum

Due to its hermetic seal and small size, the A111 is well suited to use within a vacuum chamber. In such applications care

should be taken to avoid electrical discharge near the input which can damage the unit and VOID WARRANTY

Use care in soldering leads - avoid overheating.

Pin Configuration (14 pin hybrid DIP)

Pins 1, 3, 4, 6,10, 11

Ground and case

Pin 2

V s (+4 to +10 VDC)

Pin 5

Output

Pin 7

Analog monitor

Pins 7,8

Threshold adjustment

Pin 9

No connection

Pin 12

Input

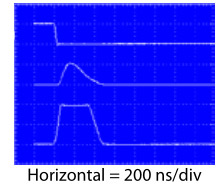

Typical Waveforms @ 25x Threshold

Top trace

Input test pulse through 2 pF capacitor. The A111 responds during the risetime of the

test pulse. Vertical scale: 100 mV/div.

Middle trace

Analog pulse, Pin 7. Vertical scale: 0.5 V/div.

Bottom trace

Discriminator output, Pin 5, driving a 1 k? load at V s = +5V. Vertical scale: 2 V/div.

Circuit Layout

Due to the high sensitivity of the A111, care should be taken in circuit layout. In general, ground plane construction is recom-mended, with all ground Pins (1,3,4,6,10,11, and 9) connected to this plane. Input and output lines should be kept well sepa-rated and in most cases shielding will be necessary. Particular attention should be paid to the detector ground connection to avoid multiple pulsing and oscillation due to feedback. The supply voltage is internally decoupled which prevents the A111 from responding to supply line transients of up to 100 mV am-plitude. While this is normally adequate, in some applications external bypassing (typically 10 nF) may be helpful. The PC21 may be used as an example of appropriate layout techniques.

Power Supply

While specifications are given for operation at +5 V, the char-acteristics of the A111 are relatively unaffected by changes insupply voltage from 4 to 10V. Parameters critical to a particularapplication should be checked at the actual operating voltage.

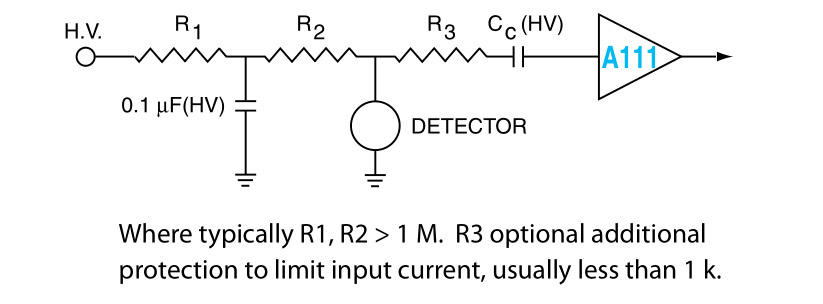

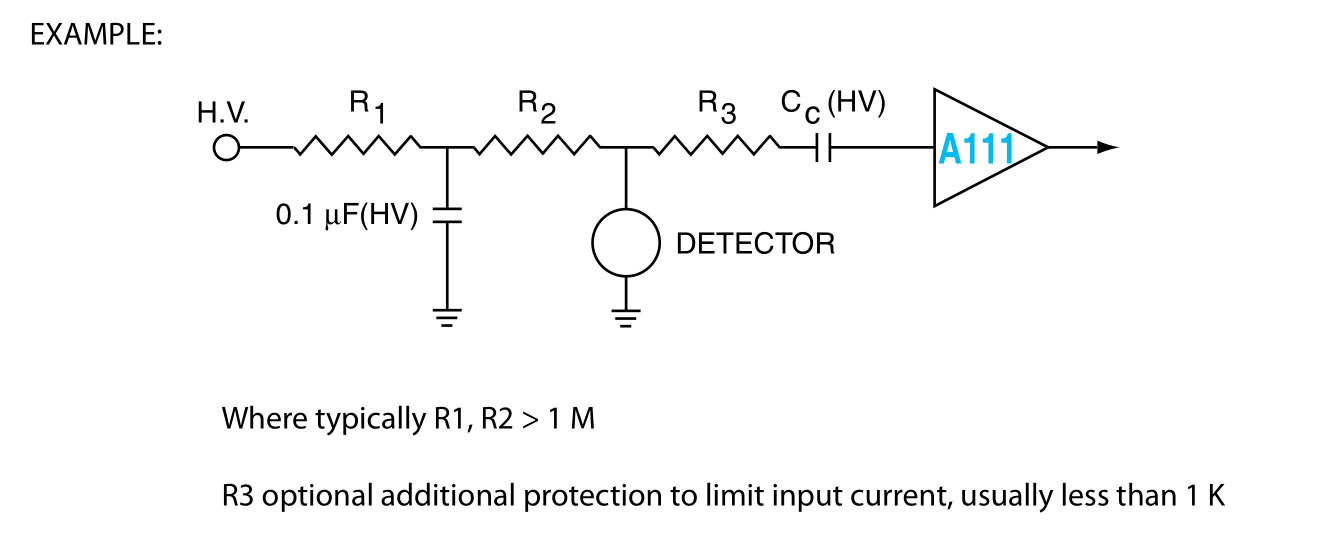

Input

The A111 has an internal input protection network, including acoupling capacitor, as shown in the diagram below. However, it is not possible to fully protect against high voltage discharge

through the input.

Example:

The A111 will respond to a negative pulse of 8 x 10 -15 cou-lombs or greater. The threshold may be increased by the con-nection of a resistor between Pins 7 and 8. Approximate values

are given in Figure 1.

While this device is optimized for negative input pulses, it will respond to positive input pulses greater than approximately 2x the negative threshold. Because the specifications provided herein apply to negative input, the user should measure all rel-evant operating characteristics for any positive-input applications.

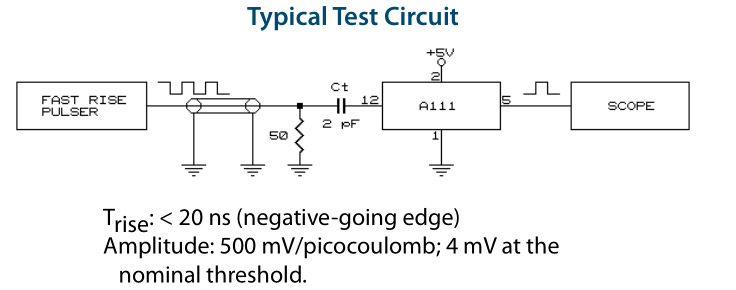

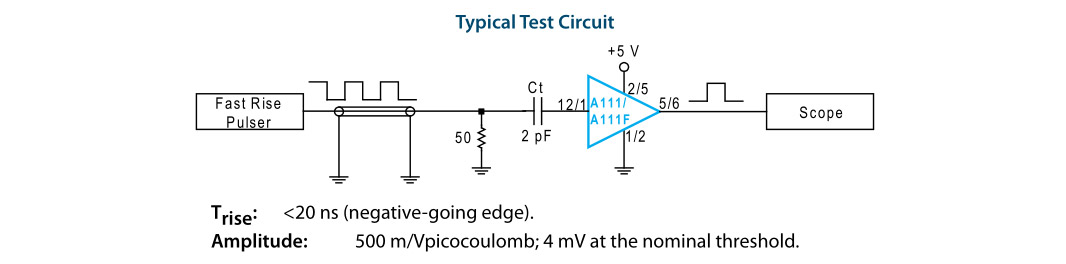

The A111 can be tested with a pulser by using a small capacitor(usually 1 or 2 pF) to inject a test charge into the input. The unit will trigger on the negative-going edge of the test pulse, which should have a transition time of less than 20 ns. This negative going edge should be followed by a relatively flat part of the waveform so that it appears as a step function. For example, a square wave is a good test waveform. (When using a square wave, it should be noted that the unit will respond to the posi-tive-going edge also, at amplitudes above 2x threshold.) Alter-nately, a “sawtooth” waveform or a tail pulse with long fall time

(> 1 μs) may be used.

Charge transfer to the input is according to Q = C t ·V, where Q= total charge, C t = value of test capacitor, and V = amplitude of voltage step. DO NOT connect the test pulser to the input

directly or through a large capacitor (> 100 pF) as this can pro-duce a large current in the input transistor and cause irrevers-ible damage.

A111 Operating Notes (con’t)

Additional Threshold Adjustment

A) Increasing the Threshold of the A111:

Increasing the threshold of the A111 beyond the 10x provided by shorting out Pins 7 and 8 can be achieved by an RC feedback as shown.

Apart from unit to unit variation, the discrimination levels willbe as follows:

1. Shorting out Pins 7 and 8 will result in 10x increase of nominal threshold: (5 x 104 electrons) x 10 =5 x 105 electrons.

2. Shorting out Pins 7 and 8 plus feedback:

R = 50 k C = 2.2 pF : 17x

R = 20 k C = 3.3 pF : 23x

R = 5 k C = 4.7 pF : 40x

R = 2 k C = 6.8 pF : 88x

Intermediate values can be obtained by adjusting the value of R.

B) Decreasing the Threshold of the A111:

Decreasing the threshold of the A111 beyond the nominal 5 x 104 electrons can be achieved by adding a resistor from Pin 8 to ground. A 300 ? resistor will approximately double

the sensitivity resulting in a threshold of 2.5 x 10 4 electrons.

Mechanical Dimensions

Applications

CAUTION for the A111

The A111 incorporates an input protection network (see specifications). However, it is not possible to fully protect against high voltage discharge through the input.

Two precautions should be kept in mind:

1) The high voltage coupling capacitor should be of sufficient voltage rating that it can-not break down under operating conditions.

2) When detector bias is turned on, the rise of high voltage at the detector should be slow enough to prevent large transient currents through the coupling capacitor into the input. This is normally provided for by a high voltage RC Filtering network with compo-nents of adequate voltage rating.

In general, it is important to avoid high voltage discharge in any part of the circuit.

| INPUTS | |

| IN | Detector Input; A111/Pin 12; A111F/Pin 1. Should be AC coupled with a high voltage capacitor (500 pF - 1000 pF). |

| DET | Provides post to connect the detector and input capacitor |

| TEST IN | Input to test circuit as described in specifications |

| Vs | A111/Pin 2; A111F/Pin 5; supply voltage (+4 to +10 VDC);supply voltage (+4 to +10 VDC) |

| H.V. | Provides post to connect the detector to the high voltage supply through a resistor |

| OUTPUTS | |

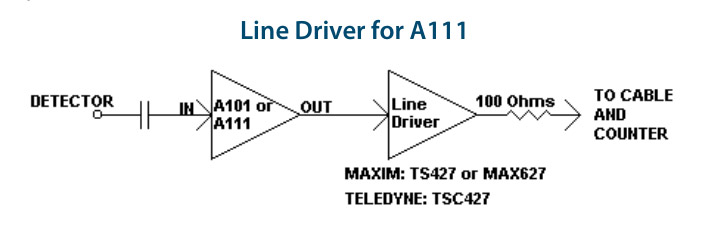

| OUT | Positive, TTL type output from A111/Pin 5; A111F/Pin 6 |

| A OUT | Positive, Analog ouput from A111/PIN 7; A111F/PIN 4 |

| BUF OUT | Positive output through a Buffer/Line Driver IC from A111/PIN 5; A111F/PIN 6. |

| COMPONENTS | |

| C1 , C2 , C3 | Filter capacitor (1 μF, 4.7 μF, 0.1 μF) |

| CT | Test capacitor (2 pF)) |

| RO | Test pulse termination (50 ?) |

| RX | External load resistor (see specifications) |

| RT | Threshold adjust resistor |

| R | Detector bias resistor (user supplied) |

| C | Detector coupling capacitor (HV) (user supplied) |

| U2 | Line Driver TPS2829 |

The A-111 or A111F can be tested with a pulser by using a small 2 pF capacitor to inject a test charge into the input. The unit will trigger on the negative-going edge of the test pulse, which should have a transition time of less than 20 ns. This negative going edge should be followed by a relatively flat part of the waveform so that it appears as a step function. For example, a square wave is a good test waveform. When using a square wave, it should be noted that the unit will respond to the positive-going edge also, at amplitudes above 2x threshold. Alternately, a “sawtooth” waveform or a tail pulse with long fall time (>1 μs) may be used.

Charge transfer to the input is according to Q = C t V, where Q = total charge, C t = value of test capacitor, and V = amplitude of volt-age step. Use only the TEST INPUT to test the A111/A111F. DO NOT connect the test pulser to the input directly or through a large

capacitor (>100 pF) as this can produce a large current in the input transistor and cause irreversible damage.

微信二維碼

微信二維碼