ADVANCED INFORMATION ONLY

? For use with Si-PIN, SDD and FAST SDD?

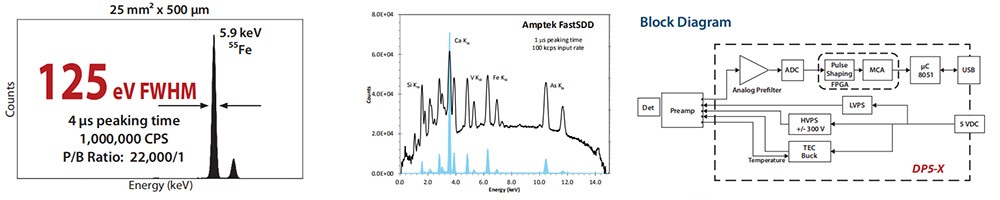

The X-55 can be provided with any of Amptek’s FastSDD? (25 mm2 or 70 mm2), standard SDD, or SiPIN (6 mm2, 13 mm2, or 25 mm2) detectors. It includes Amptek’s new DP5-X digital pulse processor, with all the capabilities of the DP5: a resolution as low at 124 eV FWHM at 5.89 keV, an output count rate over 1 Mcps, etc. The power supplies are all switching regulators for high eciency. The X-55 supports USB and RS232 communications, using the same protocol (FW6) as Amptek’s other DP5 products, and is compatible with software already developed for the DP5.

SPECIFICATIONS

| Pulse Processor | |

| Full Scale | 10 to 80 keV full scale energy for Amptek detectors. 1000 mV ADC input full scale. |

| Gain | Coarse gains of 4 and 14, fine gain with 13 bit resolution, software selectable |

| Pulse Shape | Trapezoidal |

| Peaking Time | Software selectable between 0.05 and 102 μs, e to semi-Gaussian shaping times of 0.02 to 45 μs. |

| Flat Top | 63 software selectable values for each peaking time (depends on the peaking time), > 0.05 μs. |

| Baseline Restoration | Asymmetric, 16 software selectable slew rate settings |

| Fast Channel Peaking Time | 0.05, 0.1, 0.2, 0.4, 0.8 μs (80 MHz) and 4x at 20 MHz |

| Fast Channel Pulse Pair Resolving Time | Tfast plus pulse risetime |

| Dead Time Per Pulse | 1.05 times the Tpeak + Tflat. No conversion time. |

| Maximum Count Rate | 8 x 106sec-1(periodic). Output count rate of 1.4 x 106sec-1 for a random input of 3.8 x 106sec-1(80 MHz) |

| Pulse Selection Options | Pile-up rejection, risetime discrimination, gate |

| Multichannel Analyzer | |

| Number of channels | 256, 512, 1024, 2048, 4096, or 8192 channels. |

| Bytes per channel | 3 bytes (24 bits) - 16.7M counts |

| Acquisition Time | 10 ms to 466 days |

| Conversion Time | None |

| Presets | Time, total counts, counts in ROI, counts in channel |

| MCS Timebase | 10 ms/channel to 300 s/channel |

| External MCA Controls | Gate input: Pulses accepted only when gated on by external logic. Input can be active high or active low. Software controlled. |

| Operating Modes | |

| MCA mode | Most common operating mode. The DPP acquires a pulse height spectrum, using the MCA in the FPGA, and reads this to the computer, over one of the interfaces, one software request. Readout intervals usually range from 0.1 s to a few seconds. |

| Counting mode | By reading only the status packet over one of the interfaces, one can obtain the input and output count rates at much shorter intervals than the entire spectrum can be read. Requires custom software. |

| Other modes | Supports List Mode and SCA Mode. |

| Communications | |

| USB 2.0 full speed (12 Mbps) | |

| RS-232 at 115.2k or 57.6k baud | |

| Hardware | |

| Microprocessor | Silicon Labs 8051F340 (8051-compatible core) |

| ADC | 12 bit, 80 MHz |

| Firmware | Signal processing is programmed via firmware, which can be upgraded in the field. |

| Power | |

| Nominal Input | @ +5 VDC: 700 mA (3.5 W) typical at full cooling 500 mA (2.5 W) typical with lighter cooling loads |

| Input Voltage Range | 4 V to 9 V |

| Typical Input Current | 4 V (@ 0.9 A) to 9 V (@ 0.4 A) |

| Regulator frequencies | All but HVPS > 1 MHz; HVPS: 60 kHZ |

| Power Source | External supply |

| Connectors | |

| Power | |

| USB | Standard USB Mini jack |

| Mechanical Dimensions | |

| Case size | 3.00 x 1.75 x 1.13 in (7.7 x 4.4 x 2.9 cm) |

| All dimensions are in inches except as noted | |

微信二維碼

微信二維碼